Table Of ContentProduct Order Technical Tools & Support &

Folder Now Documents Software Community

PCM1860,PCM1861,PCM1862

PCM1863,PCM1864,PCM1865

Burr-Brown Audio

ZHCSCB3D–MARCH2014–REVISEDMARCH2018

PCM186x 4 通通道道或或 2 通通道道 192kHz 音音频频 ADC

1 特特性性 2 应应用用

• 高SNR 性能: • 家庭影院和电视

1

– 110dBSNR(PCM1861/63/65) • 语音控制设备

– 103dBSNR(PCM1860/62/64) • 蓝牙®扬声器

• ADC采样率(f )=8kHz至192kHz • 麦克风阵列处理器

S

• 提供多达四个独立的ADC通道

3 说说明明

• 单端2.1V 满标量程(FS)输入

RMS

• 差分4.2V FS输入 PCM186x 系列(PCM1860、PCM1861、

RMS

• 硬件(HW)控制:PCM1860/61 PCM1862、PCM1863、PCM1864和PCM1865)音

• 软件(SW)控制(I2C或SPI): 频前端器件采用了新的音频功能集成方法,从而能够轻

PCM1862/63/64/65 松地符合欧洲生态设计法规,同时能够以更低的成本实

• 支持多达四个数字麦克风 现高性能终端产品。PCM186x 支持3.3V单电源运

(软件控制的器件) 行,并以小封装提供集成的可编程增益放大器

• 可编程增益放大器(PGA): (PGA);利用该配置,能够以更低的成本实现更小且更

– 固定增益:0dB、12dB、32dB 智能的产品。

(PCM1860/61)

PCM186x 音频前端支持从较小的mV 级麦克风输入到

– 软件控制的增益:–12dB至+32dB

2.1V 线路输入的单端输入电平,无需外部电阻分压

(PCM1862/63/64/65) RMS

器。前端混频器(MIX)、多路复用器(MUX) 和PGA 还

• 集成高性能音频PLL

支持差分(Diff)、伪差分和单端(SE) 输入,从而使这

• 3.3V单电源运行

些器件成为需要干扰抑制的产品的理想接口。

• 3.3V时的功耗:

PCM186x 集成了许多可以辅助或替代某些DSP功能

– < 85mW(PCM1860/61/62/63)

的系统级功能。

– < 145mW(PCM1864/65)

• 用于音频系统唤醒和睡眠的Energysense音频内容 集成的带隙电压基准可提供出色的PSRR,因此可能

检测器 无需专用的模拟3.3V电源轨。

• 主/从音频接口

器器件件信信息息(1)

• 自动PGA 削波抑制控制

器器件件型型号号 封封装装 封封装装尺尺寸寸((标标称称值值))

• 所有器件之间具有PCB封装兼容性

PCM186x TSSOP(30) 7.80mmx4.40mm

(1) 如需了解所有可用封装,请参阅数据表末尾的封装选项附录。

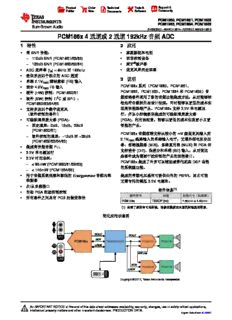

简简化化应应用用示示意意图图

IN DOUT

DOUT

MIC

BCK

PCM186x TMS320C5535 PCM5121 TPA3116

LRCK

SW mix

IN

LINE

BCK

PCM5100 TPA3116

LRCK

B

NS

IU

Copyright © 2017, Texas Instruments Incorporated

1

AnIMPORTANTNOTICEattheendofthisdatasheetaddressesavailability,warranty,changes,useinsafety-criticalapplications,

intellectualpropertymattersandotherimportantdisclaimers.PRODUCTIONDATA.

EnglishDataSheet:SLAS831

PCM1860,PCM1861,PCM1862

PCM1863,PCM1864,PCM1865

ZHCSCB3D–MARCH2014–REVISEDMARCH2018 www.ti.com.cn

目目录录

1 特特性性.......................................................................... 1 10.1 ApplicationInformation..........................................70

2 应应用用.......................................................................... 1 10.2 TypicalApplications..............................................75

3 说说明明.......................................................................... 1 11 PowerSupplyRecommendations..................... 79

4 修修订订历历史史记记录录........................................................... 2 11.1 Power-SupplyDistributionandRequirements......79

11.2 1.8-VSupport........................................................79

5 DeviceComparisonTable..................................... 7

11.3 BrownoutConditions.............................................79

6 PinConfigurationandFunctions......................... 8

11.4 Power-UpSequence.............................................80

7 Specifications....................................................... 12

11.5 LowestPower-DownModes.................................80

7.1 AbsoluteMaximumRatings....................................12

11.6 Power-OnResetSequencingTimingDiagram ....81

7.2 ESDRatings............................................................12

11.7 PowerConnectionExamples................................82

7.3 RecommendedOperatingConditions.....................12

11.8 FadeIn..................................................................83

7.4 ThermalInformation................................................12

12 Layout................................................................... 84

7.5 ElectricalCharacteristics:PGAandADCAC

Performance.............................................................13 12.1 LayoutGuidelines.................................................84

7.6 ElectricalCharacteristics:DC.................................14 12.2 LayoutExample....................................................85

7.7 ElectricalCharacteristics:DigitalFilter....................16 13 RegisterMaps...................................................... 85

7.8 TimingRequirements:ExternalClock.....................16 13.1 RegisterMapDescription......................................85

7.9 TimingRequirements:I2CControlInterface ..........17 13.2 RegisterMapSummary........................................86

7.10 TimingRequirements:SPIControlInterface .......18 13.3 Page0Registers.................................................89

7.11 TimingRequirements:AudioDataInterfacefor 13.4 Page1Registers...............................................129

SlaveMode..............................................................19 13.5 Page3Registers...............................................132

7.12 TimingRequirements:AudioDataInterfacefor 13.6 Page253Registers...........................................133

MasterMode............................................................20 14 器器件件和和文文档档支支持持................................................... 134

7.13 TypicalCharacteristics..........................................21

14.1 文档支持..............................................................134

8 ParameterMeasurementInformation................23 14.2 相关链接..............................................................134

9 DetailedDescription............................................ 25 14.3 接收文档更新通知...............................................134

9.1 Overview.................................................................25 14.4 社区资源..............................................................134

9.2 FunctionalBlockDiagrams.....................................25 14.5 商标.....................................................................134

9.3 FeaturesDescription ..............................................28 14.6 静电放电警告.......................................................134

9.4 DeviceFunctionalModes........................................60 14.7 Glossary..............................................................134

9.5 Programming...........................................................62 15 机机械械、、封封装装和和可可订订购购信信息息..................................... 135

10 ApplicationandImplementation........................ 70

4 修修订订历历史史记记录录

注:之前版本的页码可能与当前版本有所不同。

ChangesfromRevisionC(August2014)toRevisionD Page

• 已添加在该数据表中添加了PCM1860、PCM1862和PCM1864以及相关的内容;这些器件以前位于一个单独的数

据表(SLASE55A)中.............................................................................................................................................................. 1

• 已更改为清楚起见,更改了标题............................................................................................................................................ 1

• 已更改更改了特性项目以包含新的器件................................................................................................................................. 1

• 已添加添加了特性项目以阐明硬件和软件控制的器件........................................................................................................... 1

• 已更改将应用中的“汽车音响主机”更改成了“语音控制设备”................................................................................................... 1

• 已更改更改了说明部分文本以阐明3.3V电源、集成PGA和其他前端特性........................................................................ 1

• 已更改更改了简化应用图,以将以前的两个图合并为一个图................................................................................................. 1

• DeletedTypPerformance(3.3-VSupply,–1dB-FSInput)table;redundantcontent............................................................ 7

• ChangedDeviceComparisonTable;updatedforclarity........................................................................................................ 7

• Changedreferencevoltageoutputdcouplingpointtypicalvaluefrom0.5VCCto0.5AVDDinVREFpindescription........9

• ChangedXO(pin9)typefrom"—"to"Digitaloutput"inbothPinFunctionstables ............................................................. 9

• Changed"latchenable"to"wordclock"inLRCKpindescription ......................................................................................... 9

• Changedreferencevoltageoutputdcouplingpointtypicalvaluefrom0.5VCCto0.5AVDDinVREFpindescription .....11

• Changed"latchenable"to"wordclock"inLRCKpindescription ....................................................................................... 11

2 版权©2014–2018,TexasInstrumentsIncorporated

PCM1860,PCM1861,PCM1862

PCM1863,PCM1864,PCM1865

www.ti.com.cn ZHCSCB3D–MARCH2014–REVISEDMARCH2018

修修订订历历史史记记录录 (接接下下页页)

• AddedoperatingambienttemperatureandjunctiontemperaturetoAbsoluteMaximumRatingstable.............................. 12

• Changedgroundvoltagedifferencesrangefrom"AGND,DGND"to"AGNDtoDGND" ................................................... 12

• Changedstoragetemperaturemaxvaluefrom125°Cto150°C.......................................................................................... 12

• ChangedCDMvaluefrom±1500Vto±750V..................................................................................................................... 12

• Changed"Operatingjunctiontemperaturerange"to"Operatingambienttemperature,T "inRecommended

A

OperatingConditionstable................................................................................................................................................... 12

• ChangedThermalCharacteristicstabletoThermalInformationtable................................................................................. 12

• ChangedElectricalCharacteristics:PrimaryPGAandADCperformancetoincludesecondaryADCperformance

data,anddeletedseparateElectricalCharacteristics:SecondaryADCPerformancetable ............................................... 13

• Addednewtablenotetoclarifytestconditionat32-dBPGAgain....................................................................................... 13

• Addedminvalueof85dBtoinputchannelsignal-to-noiseratiofor32dB......................................................................... 13

• Changedinputchannelsignal-to-noiseratiofor32dBtypicalvaluefrom93dBto90dB.................................................. 13

• Addedminvalueof–76dBtoinputchannelTHD+N,differentialinputfor32dB .............................................................. 13

• Deleted"perinputpin"and"outofphase"fromfull-scalevoltageinputparameterinElectricalCharacteristics................13

• Changedinputchannelsignal-to-noiseratio,single-endedinputvalueforPCM1865from110dBto106dB;

differentialconditionsusedpreviously.................................................................................................................................. 13

• Changed"EnergysenseDetectionThreshold"to"DefaultEnergysenseSignalDetectionThreshold"inElectrical

Characteristics,SecondaryADCPerformance.................................................................................................................... 13

• ChangedsecondaryADCsamplingratefrom"sameasaudiosamplingrate"tominof8kHzandmaxof192kHz.........13

• ChangedElectricalCharacteristics,DCconditionsfrommastertoslavemode;systemclockfrom256×f to512xf ....14

S S

• ChangedPOWERsectionoftheElectricalCharacteristics,DC;updatedsectionstructureforclarity................................ 14

• DeletedallrowswithXTALascondition;notrequiredfornormaloperation....................................................................... 14

• DeletedallrowswithPowerdown;notavalidoperatingmode ........................................................................................... 14

• ChangedAVDDcurrenttypvaluefor2-channel,3.3-V,activemodefrom16mAto18mA.............................................. 14

• ChangedTotalpowervaluefor2-channel,3.3V,sleepmodefrom24mWto17.6mW.................................................... 14

• ChangedDVDDcurrentfor2-channel,3.3V,standbymodefrom353µAto0.015mA..................................................... 14

• ChangedTotalpowerfor2-channel,3.3V,standbymodeforsoftwaredevicefrom0.59mWto0.64mW ...................... 14

• DVDDcurrentfor2-channel,3.3Vand1.8Vactivemodetypvaluefrom10µAto0.015mA.......................................... 14

• ChangedTotalpowerfor2-channel,3.3Vand1.8Vactivemodefrom68mWto69.2mW............................................. 14

• ChangedTotalpowerfor4-channel,3.3V,activemodefrom145mWto135.3mW ....................................................... 14

• ChangedTotalpowerfor4-channel,3.3Vand1.8V,activemodefrom128mWto117.3mW........................................ 15

• Deletedredundanttext"Validwithrecommendedvaluesonanalograils(AVDD,VREF,andsoon)"fromPSRR...........15

• Changed"HPFfrequencyresponse"to"HPF–3-dBcutofffrequency"inElectricalCharacteristics:DigitalFilter..............16

• AddedmaximumBCKfrequencyrowstoTimingRequirements,ExternalClocktable....................................................... 16

• ChangedallFFTplotXaxesfromlogscaletolinearscale................................................................................................. 21

• AddedFigure7..................................................................................................................................................................... 21

• ChangedFigure9................................................................................................................................................................. 21

• DeletedpreviousFigure11andFigure12........................................................................................................................... 21

• AddedFigure11................................................................................................................................................................... 21

• AddedFigure13................................................................................................................................................................... 22

• AddedFigure15................................................................................................................................................................... 22

• ChangedOverviewsectionforclarity................................................................................................................................... 25

• DeletedTerminologysection;movedcontenttoOverviewsection...................................................................................... 25

• AddedFeatureDescriptionsection,andmovedexistingcontenthere................................................................................ 28

• ChangedtextinAnalogFrontEndsectionforclarity........................................................................................................... 28

• ChangedMicBiassection;internalresistorisaterminatingresistor................................................................................... 29

版权©2014–2018,TexasInstrumentsIncorporated 3

PCM1860,PCM1861,PCM1862

PCM1863,PCM1864,PCM1865

ZHCSCB3D–MARCH2014–REVISEDMARCH2018 www.ti.com.cn

修修订订历历史史记记录录 (接接下下页页)

• DeletedFigure21andFigure22fromMicBiassection...................................................................................................... 29

• AddednotestatingthatclocksarerequiredtoberunninginordertochangePGAintheProgrammableGain

Amplifiersection................................................................................................................................................................... 31

• AddedtexttoclarifydigitalPGAupdateuseinProgrammableGainAmplifiersection....................................................... 31

• Changednotetoclarifythatthefullscalemovesto4.2V whenindifferentialmodeattheendofthe

RMS

ProgrammableGainAmplifiersection.................................................................................................................................. 31

• AddednewparagraphtoendofStereoPCMSourcessection............................................................................................ 33

• ChangedFigure33;clocktreeupdatedandcorrected........................................................................................................ 36

• AddednewparagraphtotargetADC,DSP1andDSP2clockratesinDeviceClockDistributionandGenerationsection 36

• ChangedClockConfigurationandSelectionsection;relevanttohardware-controlleddevicesonly.................................. 37

• AddednewparagraphregardingregisterMST_SCK_SRCtoClockSourcesforSoftware-ControlledDevicessection....37

• Addednote("InMasterModeon..")toClockSourcesforSoftware-ControlledDevicessection........................................ 38

• ChangedTable7;updateddescriptionsforclarity............................................................................................................... 38

• Changed"CLK_DIV_MST_SCK"to"CLK_DIV_SCK_BCK"and"CLK_DIV_MST_BCK"to"CLK_DIV_BCK_LRCK"

inTable7.............................................................................................................................................................................. 38

• ChangedFigure34;clocktreeupdatedandcorrected........................................................................................................ 38

• Added"TargetClockRatesforADC,DSP#1andDSP#2"section..................................................................................... 39

• ChangedTable9;correctedPLLvaluesbyincreasingPandRby1,andcorrectedDSP1clockdividervalues..............40

• ChangedTable10;correctedPLLvaluesbyincreasingPandRby1,andcorrectedDSP1clockdividervalues............41

• ChangedTable12;correctedPLLvaluesbyincreasingPandRby1,andcorrectedtypoinDSP2columntitle..............43

• ChangedTable13;correctedPLLvaluesbyincreasingPandRby1,andcorrectedtypoinDSP2columntitle..............44

• Addedtext"Theclocktreemustalsobeset..."toSoftware-ControlledDevicesADCNon-AudioMCKPLLMode

section.................................................................................................................................................................................. 45

• ChangedPLLconditionforD=0000toshow1MHz≤(PLLCKIN/P)≤20MHzand1≤J≤63...................................... 45

• ChangedPLLconditionforD≠0000toshow6.667MHz≤(PLLCLKIN/P)≤20MHzand4≤J≤11............................. 45

• ChangedregisternumbersinSoftware-ControlledDevicesManualPLLCalculationsectiontoalignwiththeregister

numbersinTable14............................................................................................................................................................. 46

• ChangedClockHaltandErrorsection;clockerrormovedtoClockssection,andinterruptcapabilitydeleted...................46

• AddedChangingClockSourcesandSampleRatessection............................................................................................... 47

• ChangedSecondaryADC:EnergysenseandAnalogControlsection;energysensesignaldetectionnotavailablein

activemode.......................................................................................................................................................................... 48

• Changedtextfrom"controlsignalsupto1.65V"to"controlsignalsupto4.3V"intheSecondaryADCAnalogInput

Rangesection....................................................................................................................................................................... 49

• Changedsectiontitlefrom"SecondaryADCDCLevelChangeDetection"to"SecondaryADCControlsenseDC

LevelChangeDetection"...................................................................................................................................................... 49

• AddedtexttotheSecondaryADCControlsenseDCLevelChangeDetectionsection;controlsenseisavailablein

bothactiveandsleepmodes................................................................................................................................................ 49

• AddeddetailstotheSecondaryADCControlsenseDCLevelChangeDetectionsectionregardinghowtoread

simple8-bitvaluesfromthesecondaryADC....................................................................................................................... 49

• AddednewsecondparagraphtoEnergysensesection....................................................................................................... 50

• ChangedparagraphafterFigure38inEnergysenseSignalLossFlagsectionforclarity................................................... 51

• ChangedDigitalDecimationFilterssection;clarifiedtwodifferentHPFsinthedevice....................................................... 53

• ChangedtexttoclarifydigitalPGAupdateuseinDigitalPGAsection................................................................................ 53

• ChangedInterruptControllersection;deletedclockerrorasaninterruptsource................................................................ 56

• ChangedtextafterFigure44inInterruptControllersection;clarifiedINTpinsallhavesamelogicsignal......................... 56

• AddedshortdescriptionintheDINToggleDetectionsection.............................................................................................. 56

• AddedClearingInterruptssection........................................................................................................................................ 56

• ChangedDigitalAudioOutput2Configurationsection;DOUT2notavailableinTDMmode,onlyfor4-chdevices..........58

4 版权©2014–2018,TexasInstrumentsIncorporated

PCM1860,PCM1861,PCM1862

PCM1863,PCM1864,PCM1865

www.ti.com.cn ZHCSCB3D–MARCH2014–REVISEDMARCH2018

修修订订历历史史记记录录 (接接下下页页)

• AddedTimeDivisionMultiplex(TDMSupport)section........................................................................................................ 58

• ChangedlocationoftimingdiagramstoSpecificationssection,anddeletedInterfaceTimingsection............................... 59

• ChangedtextinBypassingtheInternalLDOtoReducePowerConsumptionsectiontoclarifyTDMmodewith1.8-V

IOVDDoperation.................................................................................................................................................................. 61

• Addedtext"TheI2Ccontrolport.."totheI2CInterfacesection............................................................................................ 64

• ChangedpinnumbersinTable22from"15,16,14"to"23,24,25"................................................................................... 64

• AddedRealWorldSoftwareConfigurationusingEnergySenseandControlsensesection................................................. 65

• AddedmoredetailtoProgrammingDSPCoefficientsonSoftware-ControlledDevicessection,andmovedtonew

location................................................................................................................................................................................. 68

• 已添加DualPCM186xTDMFunctionalitysection............................................................................................................... 73

• 已添加newparagraphtoendofAnalogFront-EndCircuitForSingle-Ended,Line-InApplicationssection.......................74

• 已更改1.8-VSupportsection;clarifiedthatbothIOVDDandLDOmustbedrivenwith1.8Vin1.8-Vmode.................... 79

• 已添加BrownoutConditionssection.................................................................................................................................... 79

• 已添加testconditiontostep3inPowerUpSequencesection;(PLLrequires<250µs)................................................... 80

• 已更改Layoutsectionforclarity .......................................................................................................................................... 84

• 已删除oldFigure67,PCM1865EVMSignalPartitioning;redundant,andsameinformationshowninFigure74 ............84

• 已添加Figure75................................................................................................................................................................... 85

• 已更改"0xFF"to"0xFE"inlastsentenceofRegisterMapDescriptionsection................................................................... 85

• Changedvaluesforregister3,bits6-0;changedfrom"RSV"tocorrectbitnames ........................................................... 86

• Changedbits4and3from1and0toRSV,respectively,inregister27............................................................................. 86

• Changedregister44(0x2C)fromreserved("RSV")toactualbitnames............................................................................. 87

• Changedregisters52and53toregisters51and52,respectively...................................................................................... 87

• ChangedTX_WLENbitoption00descriptionfrom"Reserved"to"32-bit"inPage0,register11...................................... 95

• ChangedGPIO0_FUNCfor001from"SPIMISO(Out:Default)"to"DigitalMICInput0(In)"andfor010from

"RESERVED"to"SPIMISO(Out)"inregister16................................................................................................................ 98

• Changed"DPGA"to"APGA"indescriptioncolumnforbits3,2,1,and0inregister25.................................................. 104

• ChangedDIV_NUMdefaultvalueinpage0,register33from"0000001"to"0000000"................................................. 106

• Changednamesanddescriptionsofmastermodeclockdividersinregisters37,38,and39forclarity.......................... 108

• Changed"Divider"to"Multiplier"inR[3:0]descriptionforregister42................................................................................ 110

• ChangedvaluesforR[3:0]from1,1/2,1/3,1/4,and1/16to1,2,3,4,and16,respectively .......................................... 110

• Changed"Divider"to"Multiplier"inJ[5:0]descriptionforregister43................................................................................ 111

• Changed"Divider"to"Multiplier"inD_LSB[7:0]descriptionforregister44....................................................................... 111

• Changed"Divider"to"Multiplier"inD_MSB[5:0]descriptionforregister45...................................................................... 111

• Changedregister52toregister51..................................................................................................................................... 114

• Changedregister53toregister52..................................................................................................................................... 115

• Changedbit3fromCLKERRtoRSVinregister96........................................................................................................... 123

• Deletedbit3fromCLKERRtoRSVinregister97............................................................................................................. 124

• Changeddefaultvaluesinpage1:register1forbits4,2,1,and0from"1"to"0",andupdateddescriptionsforclarity.129

ChangesfromRevisionB(March2014)toRevisionC Page

• 已更改在整个数据表中将“端子”更改成了“引脚”...................................................................................................................... 1

• 已添加添加了有关可订购产品附录的表注.............................................................................................................................. 1

• 已删除从“器件信息”表的部件号中删除了封装符号................................................................................................................. 1

• 已更改将“-1dBFS下的THD+N”更改成了“-1dBFS下的差分输入”......................................................................................... 1

• CorrectedpinnumbersinPinDescriptiontable..................................................................................................................... 9

版权©2014–2018,TexasInstrumentsIncorporated 5

PCM1860,PCM1861,PCM1862

PCM1863,PCM1864,PCM1865

ZHCSCB3D–MARCH2014–REVISEDMARCH2018 www.ti.com.cn

• CorrectedpinnumbersinPinDescriptiontable-pin11isLDOandpin12isDGND........................................................ 11

• ChangedEnergysenseAccuracytypfrom1dBto3dB........................................................................................................ 13

• ChangedSecondaryADCAccuracyfrom10bitsto12bits ............................................................................................... 13

• AddedParameterMeasurementInformationsection .......................................................................................................... 23

• 已添加defaultvaluesforreservedregisters........................................................................................................................ 85

ChangesfromRevisionA(March2014)toRevisionB Page

• 已添加添加了PCM1861示例系统图..................................................................................................................................... 1

• 已更改更改了典型性能表....................................................................................................................................................... 1

• UpdatedPage3andPage253registers ............................................................................................................................ 85

ChangesfromOriginal(March2014)toRevisionA Page

• 已更改将“预告信息”更改成了“生产数据”状态......................................................................................................................... 1

6 Copyright©2014–2018,TexasInstrumentsIncorporated

PCM1860,PCM1861,PCM1862

PCM1863,PCM1864,PCM1865

www.ti.com.cn ZHCSCB3D–MARCH2014–REVISEDMARCH2018

5 Device Comparison Table

PARTNUMBER PCM1860 PCM1861 PCM1862 PCM1863 PCM1864 PCM1865

Controlmethod H/W I2CorSPI

Differential

SNRperformanceAweighted 103dB 110dB 103dB 110dB 103dB 110dB

data

Analogfrontend 2.1VRMSMUXwithfixedPGAgains 2.1VRMSMUX,MIX,PGAandauxiliaryADC

Simultaneouschannel

2 2 4

capability

Energysensesignaldetect Yes(fixedthreshold) Yes(programmablethreshold)

Energysensesignalloss No Yes(programmablethreshold)

Controlsense No Yes(programmablethreshold)

Interruptcontroller No Yes

Digitalmicrophonesupport No Yes(2) Yes(4)

ClockPLL BCKtogenerateinternalmasterclock Fullyprogrammable

Lowestpowerstandbymode

7.96mW 0.22mW

(1.8-VIOVDD)

Digitalmixingwithdigitaland

No Yes

analoginputs

Digitaloutputformats Left-justified,I2S Left-justified,right-justified,I2S,TDM

Energysensesignallossanddetect,controlsense,postPGAclipping,RXdigital

Interruptcapabilities Energysensesignaldetect

toggle

Copyright©2014–2018,TexasInstrumentsIncorporated 7

PCM1860,PCM1861,PCM1862

PCM1863,PCM1864,PCM1865

ZHCSCB3D–MARCH2014–REVISEDMARCH2018 www.ti.com.cn

6 Pin Configuration and Functions

DBTPackage:PCM1860andPCM1861

30-PinTSSOP

TopView

VINL2/VIN1M 1 30 VINR3/VIN3P

VINR2/VIN2M 2 29 VINL3/VIN4P

VINL1/VIN1P 3 28 VINR4/VIN3M

VINR1/VIN2P 4 27 VINL4/VIN4M

Mic Bias 5 26 MD0

VREF 6 25 MD1

AGND 7 24 MD3

AVDD 8 23 MD2

XO 9 22 MD4

XI 10 21 MD5

LDO 11 20 MD6

DGND 12 19 INT

DVDD 13 18 DOUT

IOVDD 14 17 BCK

SCKI 15 16 LRCK

Not to scale

8 Copyright©2014–2018,TexasInstrumentsIncorporated

PCM1860,PCM1861,PCM1862

PCM1863,PCM1864,PCM1865

www.ti.com.cn ZHCSCB3D–MARCH2014–REVISEDMARCH2018

PinFunctions:PCM1860andPCM1861

PIN

TYPE DESCRIPTION

NO. NAME

1 VINL2/VIN1M Analoginput Analoginput2,L-channel(ordifferentialMinputforinput1)

2 VINR2/VIN2M Analoginput Analoginput2,R-channel(ordifferentialMinputforinput2)

3 VINL1/VIN1P Analoginput Analoginput1,L-channel(ordifferentialPinputforinput1)

4 VINR1/VIN2P Analoginput Analoginput1,R-channel(ordifferentialPinputforinput2)

5 MicBias Power Microphonebiasoutput

Power Referencevoltageoutputdecouplingpoint(typically,0.5AVDD).Connect1-µFcapacitor

6 VREF

fromthispintoAGND.

7 AGND Power Analogground

Power Analogpowersupply(typically,3.3V).Connect0.1-µFand10-µFcapacitorsfromthispin

8 AVDD

toAGND.

9 XO Digitaloutput Crystaloscillatoroutput

10 XI Digitalinput Crystaloscillatorinputormasterclockinput(1.8-VCMOSsignal)

Power Internallow-dropoutregulator(LDO)decouplingoutput,orexternal1.8-Vinputtobypass

11 LDO

LDO.Connect0.1-µFand10-µFcapacitorsfromthispintoDGND.

12 DGND Power Digitalground

Power Digitalpowersupply(typically,3.3V).Connect0.1-µFand10-µFcapacitorsfromthispinto

13 DVDD

DGND.

14 IOVDD Power PowersupplyforI/Ovoltages(typically,3.3Vor1.8V).

15 SCKI Digitalinput CMOSlevel(3.3V)masterclockinput

Digital Audiodatawordclock(leftrightclock)input/output(1)

16 LRCK

input/output

Digital Audiodatabitclockinput/output(1)

17 BCK

input/output

18 DOUT Digitaloutput Audiodatadigitaloutput

19 INT Analogoutput Interruptoutput(foranaloginputdetection).Pullhighforactivemode,pulllowforidle.

Analoginput AnalogMUXandgainselectionusingMD6,MD5,andMD2pins,respectively:

000:SECh1(VINL1andVINR1)

001:SECh2(VINL2andVINR2)

010:SECh3(VINL3andVINR3)

20 MD6 011:SECh4(VINL4andVINR4)

100:SECh4with12-dBgain

101:SECh4with32-dBgain

110:DiffCh1(VIN1PandVIN1M,VIN2PandVIN2M)

111:DiffCh2(VIN3PandVIN3M,VIN4PandVIN4M)with12-dBgain

21 MD5 Analoginput AnalogMUXandgainselection(seeMD6pinfordescription)

22 MD4 Analoginput Audioformat:high=left-justified,low=I2S

23 MD2 Analoginput AnalogMUXandgainselection(seeMD6pinfordescription)

24 MD3 DigitalInput Filterselect:0=FIRdecimationfilter,1=IIRlowlatencydecimationfilter

Analoginput AudiointerfacemodeselectionusingMD1andMD0pins,respectively:

00:Slavemode,256×f ,384×f ,512×f autodetect

S S S

25 MD1 01:Mastermode(512×f )

S

10:Mastermode(384×f )

S

11:Mastermode(256×f )

S

26 MD0 Analoginput Audiointerfacemodeselection(seeMD1pinfordescription)

27 VINL4/VIN4M Analoginput Analoginput4,L-channel(ordifferentialMinputforinput4)

28 VINR4/VIN3M Analoginput Analoginput4,R-channel(ordifferentialMinputforinput3)

29 VINL3/VIN4P Analoginput Analoginput3,L-channel(ordifferentialPinputforinput4)

30 VINR3/VIN3P Analoginput Analoginput3,R-channel(ordifferentialPinputforinput3)

(1) Schmitttriggerinputwithinternalpull-down(50kΩ,typically).

Copyright©2014–2018,TexasInstrumentsIncorporated 9

PCM1860,PCM1861,PCM1862

PCM1863,PCM1864,PCM1865

ZHCSCB3D–MARCH2014–REVISEDMARCH2018 www.ti.com.cn

DBTPackage:PCM1862,PCM1863,PCM1864,andPCM1865

30-PinTSSOP

TopView

VINL2/VIN1M 1 30 VINR3/VIN3P

VINR2/VIN2M 2 29 VINL3/VIN4P

VINL1/VIN1P 3 28 VINR4/VIN3M

VINR1/VIN2P 4 27 VINL4/VIN4M

Mic Bias 5 26 MD0

VREF 6 25 MS/AD

AGND 7 24 MC/SCL

AVDD 8 23 MOSI/SDA

XO 9 22 MISO/GPIO0/DMIN2

XI 10 21 GPIO1/INTA/DMIN

LDO 11 20 GPIO2/INTB/DMCLK

DGND 12 19 GPIO3/INTC

DVDD 13 18 DOUT

IOVDD 14 17 BCK

SCKI 15 16 LRCK

Not to scale

NOTE:TheDMIN2optionforpin22isonlyavailableonthePCM1864andPCM1865devices.

10 Copyright©2014–2018,TexasInstrumentsIncorporated

Description:I2C or SPI. 110dB Differential. 1 or 2VRMS MUX, Mix, PGA and Aux ADC. 2. 1 or 2VRMS MUX, Mix, PGA and Aux ADC,. PCM1865. I2C or SPI over operating temperature range (unless otherwise noted). PARAMETER. TEST CONDITIONS. MIN. TYP. MAX. UNIT. RthJA. Theta JA. High K. 91.2. ψJT.